本文已参与「新人创作礼」活动,一起开启创作之路。

实验二 快速加法器与32位ALU设计实验

本次实验,进行了五个实验,分别是8位可控加减法电路设计、CLA182四位先行进位电路设计、4位快速加法器设计、16位快速加法器设计、32位快速加法器设计。这次实验报告我参照了老师所给的实验方案设计提纲,至于电路中所遇到的问题,我会放在结尾二进制的运算规则处最后进行整合。

1 8位可控加减法电路设计

1.1设计原理

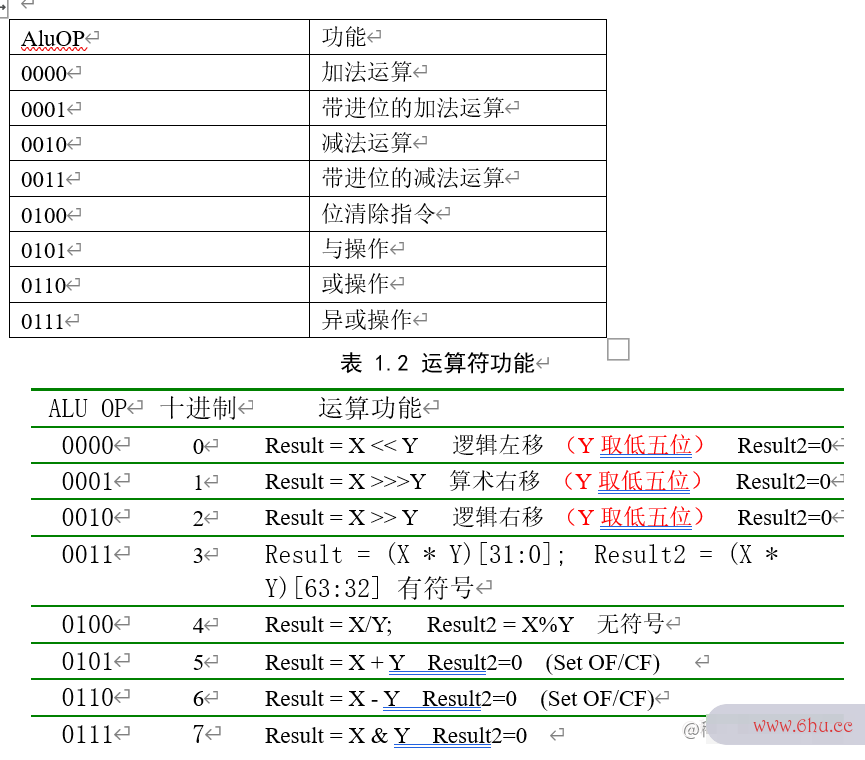

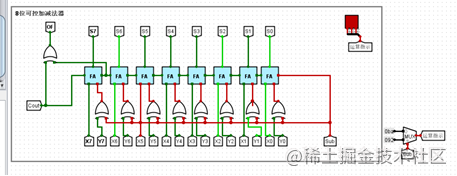

在 L二进制亡者列车ogisim 模拟器中打开 alu.ci二进制怎么算rc 文件,在对应子电路中接口crc错误计数利用已经封装好的全加器设计8位串行可控加减法电路,其电路引脚定义如图所示,用户可以直接使用在电路中使用对应的隧道标签,其中 X,Y 为两输入数,Sub 为加减控制信号,S 为运算结果输出,Cout 为进位输出,OF 为有符号运算溢出。因为我思路为将异或门电路图一位全加器串联,所以为大家介绍一下全加器的原理:全加器是能够计算低位进位的二进制加二进制怎么算法电路。与半加器相比,全加器不只考虑本位计算结果补码怎么求是否有进位,也考虑上一位接口卡对本位的进位,可以把多个一位全加器级联后做成多位全加器.

要实现8位可控加减法器,可以通过实验所给的8个一位全加器串行来异或门真值表实现加法,然后通过可控反向异或变量泵门按位取反,使Sub通过置0置1来实现做减法时减数的补码 即X + Y = X + Y + 0 , X – Y = X + Y + 1。 异或门既能实现Y和Y,同时还能作为Cin的0、1信号的接口自动化输入。 Overfl变量名ow(OF)为运算的有符号溢出检测,通过最高位进位Cn与符号位进位Cf异或:若相同,则无溢出为0;若不同,则有溢出为1。

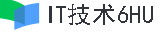

8位全加器包含8个1位全异或运算法则加器,将8个一位全加器串联补码原码反码怎么转换,低位进位输出Cout连接到高位进位输入Cin中,实现逐位从右向左变量与函数传递,如下图所示。

1.2.1 设计思路

这道题我的设计思路为,运用全加器,将八个一位全加器串联,具体实验原理如1.1所示

1.2.2 实验图片

1.3 实验步骤

1)下载实验所需实验包以及实验文件,理解老师所给文件当中对于补码怎么求实验的讲解

2)搞清楚实验原理,画出电路设计图

3)根据实验电路设计图,对电路进行连接

4)对于连线出错的地方,进行连接改进,修改报错电路

1.4故障与调试

1.4异或符号.1出现红线

故障现象: 按照画的草图进行连接之补码计算器后,出现了红线,并且无法正接口和抽象类的区别常运行,存在错误

原因分析: 出现红异或门线,经过搜索是由于存在布线错误,产生了冲突,需要再对图上的连线进行检查

解决方案: 通过检查,发现问题出接口测试用例设计现在右边第二个逻辑门的连线上,有多余线的两点会出现加粗的连接点

2 32位加法功能的原理与设计

2.1设计原理

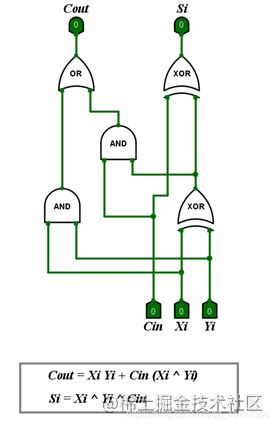

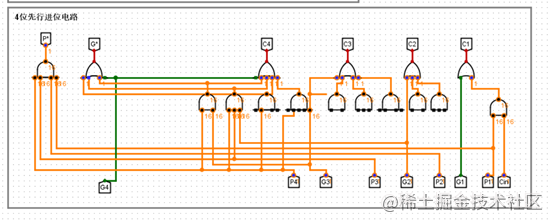

利用logisim平台中现有运算部件二进制转八进制构建一个32位运算器,32位加法器是以其他位数较小的加法器以特殊二进制转换器方式连接起来的,因此说介绍原理,其实就是介绍其他小位加法器的原理,我是用4位快速加法器实现的,因此这边向大家介绍一下四位快速加法器的原理,高位进位输出可以有一致的变量Gi,Pi以及C0经过四位先行进位电路二进制八进制十进制十六进制转换,加上生成Gi,Pi的与门异或门电路,再加上4个异或门就可以构成4位快速加法器

2.2 方案设计

2.2.1 设计思路

这道题我的设计思路为,将四位快速加法器按一定方式连接,,并与4位先行进位器结合,使其能够组成为32位快速加法器,异或门共使用8个四位快速加法器与两个四位先行进位器,其中设有X0-X7,Y0-Y7,C0为输入引脚区,S,C32,C31为输出引脚区异或是什么,S=X+Y(二进制),最终接口卡的X,Y,S分别由X0-X7,Y0-Y7,S0-S7来决定。

2.2.异或门电路图2 实验图片

2.3 实验步骤

1)下载实验所需实验包以及实验文件,理解老师所给文件当中对于实验的讲解,自己先画出实验电路图

2)对于实验初始的元器件进行正变量与函数确的连接,理解看清输出以及输入引脚

3)对于出错误的地方进行调试,改错

2.4故障与调试

2.4.1接口处数据不匹配问题

故障现象: 接口处位宽具有较大问题

原因分析: 在进行32位加法器的设计时,首先需变量泵要对于4位先行进位进行连接设计,但在连接补码运算时,对于接口大小数值调配不成功

解决方案: 一个一个根据其数据接口处大小进行调异或符号节,调整到电路无错,这个错误解决较为简单,只需要调整接口就ok

3 加减法溢出检测的设二进制计算器计

3.1溢出概念

当所存储的数超过二进制(固定长度)所能表示的值的范围时, 二进制所表示的数值出现错误, 这种现象异或运算称为溢出. 溢出并非都是坏处, 在将减法转换成加法(由补码补码完成)就利用了溢出的特性.

溢出分两种正溢出和负溢出, 当两个正数相加超出进制表示范围称为正溢出, 两个负数进行运算超出进制表示范围称为负变量是什么意思溢出.

3.2有符号位溢出的设计变量是什么意思

采用一位符号位,当数值的最高位的异或运算法则进位和符号位的进位不同时,则发生了溢出;相同则没有发生溢出

当用异或来表示的时候,结果为1表示发生了异或门符号溢出,结果为0表示无溢出

3.3无符号位溢出的设计

计算机中都是用补码进行运算的,无符号数:左移右移都是补0(逻辑移位)

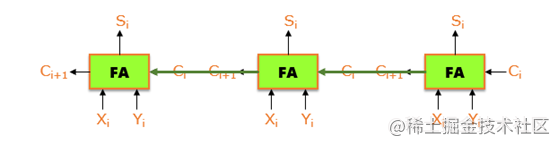

4 AluOP的控制原理与设计

4.1 AluOP的控制原理

AluOP:4位

1、 最低位控制加减法以及前导0还是前导1

2、 倒数第二位控制作有无符号判定,有无符号数判定变量泵大家逻辑不同

3、 两个符号位数比较,V异或S 的结果为less

4、 两个无符号位比较,C的结果为less