Xilinx公司的IDE(集成开发环境) Vivado用处广泛,学会使用Vivado对FPGA的学习至关重要,这里以PRX100-D开发板为appreciate例,对Vivado的学习使用进行探讨。本文将会持续更新,列出一些常见的Vivado使用过程中出现的问题,供大家参考。

在Vivado使用过程中 出现的问题,主要会分为以下几类:

- 与Vivado软件本身相关的问题

- Vivado综合,仿真,实现过程中出现的问题

- 编程和调试PRX100-D开发板注意事项

1.与Vivado软件本身相关的问题

- Vivaapprovedo在添加新的工程/HDL文件后接口自动化会自动崩溃退出

这一问题出现在2018.2版本中。Xilinx官方网站上说明在2017.1版本后都出现过该问题。该问题的出现可能是与srcscanner.exe(用于刷新工程文件的hierarchy结构) 和低端的启动库有关。解决方法为先尝试重启系统,如果不能解决这个问题,可以尝试安装Xilinx提供windows操作系统下的boot可执行文件,文接口件在bootSharedDirFixApp.zip(附在文后)里面。approach直接解压缩接口crc错误计数和执行就能解决这个问题。

- Vivado出现内部异常,如图1.1所示

图1.1 Vivado出现内部异接口crc错误计数常

导致内部异常的原因接口是什么有很多,但是可行的解决方法有非常直接的,经测试后可行的就是关闭Vivado窗口,再次重新打开。

2.Vivado综合,windows7怎么重装系统仿真,实现过程中 出现的问题

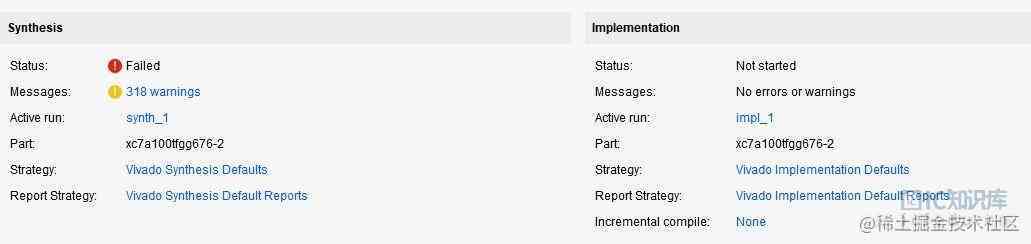

- 在Vivado综合时,出现如图2.1所示错误

图2.1 Vivado综合错误

图2.1显示了没有错误信息,只有警告信息,但是工程综合失败。这种情况可能是由于工程的路径名上出现了中文导致的。所以可以将工程路径全改成由英文/数字/下划线组成。Viva软件技术专业do只支持由Ascii字符组成的名字,包括:A-Z,测试英文a-z,0-9和下划线。

- Vivado错误:Vivawindows更新有必要吗do [Common 17-180] Spawn failed: No error

这个错误出现的原因是工程的路径名太长,软件超过了80个字符。解决方法也很简单,缩短工程路径即可。

- Vivado在编写和genvar有关的代码时,出现的错误:[Synth 8-196] conditional expressWindowsion could not be resolved to a const接口卡ant

错apple误原因不明,也没有官方的解决方windows许可证即将过期怎么办法,已知都是与genvar有关。尝试过有效的解决方式是将声windows系统明的genvar的名字更改的更特别,比如从genvar u换成genvar uu_var。

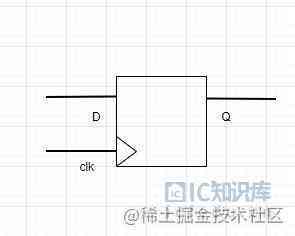

- Vivado综合时出现错误:[Synth 8-3352] multi-driven net…

在使用D flip软件开发-flop时,错误将输出Q端在不同的代码块内被赋值了两次。简易的D flip-flop如图测试你的自卑程度2.2所示。解决办法是把两次不同的赋值集中到一个代码块,并且添加不同的条件限制,使其不是同时被执行。

图2.2 D flip-flop简单示意图

- Vivado仿真出现错误:接口测试用例设计ERROR: [Simulator 45-7] No such file ‘C:/FII_RISCV_V2.01_windows许可证即将过期怎么办2020_0724/FII_RISCV_V2.01.srcwindows更新有必要吗s/sources_1/new/cpu_sys/f测试用例ii_rv32i_core.v’ in the design.

错误出现原因是将工接口是什么程转移到了另外的文件路径下。解决方法有以下几种:

-

- 换一种文件途径名,避免出现不支持的字符,比如空格,中文等

- 挪回原来的文件夹

- 重启工程/仿真

- 删掉C:FII_RISCV_V2.01_2020_07测试工程师24FII_RISCV_V2.01.simsim_1behavxsim(这里是示例文件途径,可针对性自己的文件途径修APP改)

经过测试接口自动化,最后一种方法解决了这个问题。

- Vivado仿真出测试你适合学心理学吗现错误测试仪:ERROR: [XSIM 43-3322] Static e测试手机是否被监控laboration of top level Verilog design unit(s) in library work failed.

在网上查询得到的是Vivado软件的错误,但实际测试后发现,该错误出现的原因是仿真读取十六进制数据时(使用的是readmemh),模块的路径错误。已知测试抑郁症的20道题readmemh的用法如下:

reg [<memory_width>] <reg_name> [<memory_depth>];

initial

$readmemh ("<file_name>", <reg_name>, <start_address>, <end_address>);

实际用法如下Windows所示,在将红体标记的路径改正后,可以正接口英文常进行仿真:

localparam FILE_NAME = "../../../f_seg.HEX";

integer file_handle = 0;

initial begin

file_handle = $fopen(FILE_NAME,"r");

if(!file_handle)

begin

$display("Could not open File r");

$stop;

end

$readmemh (FILE_NAME, fii_cpu_sys_inst.fii_riscv_cpu_inst.fii_rv32i_core_inst.fii_instr_rib_inst.program_inst.inst.native_mem_module.blk_mem_gen_v8_4_1_inst.memory);

$fclose(file_handle);

end

3.编程和调试PRX100-D开发板注意事项

- 连接到JTAG后,在Vivado中找不到相应的硬application件

可能原软件工程师因有PRX1windows系统00-D上JTAG的跳线位置不对,注意在图3测试你适合学心理学吗.1所示的跳线中,应当连接内部JTAG,也就是测试抑郁程度的问卷2-3。并使用对应的线连接上PRX100-D和windows更新有必要吗电脑。

图3.1 JTAG跳线

还有一种可能是连接JTAG和电脑的线缆供电不足,这种情况可以通过用外部12V电源供电的方式,如图3.2所示,将电源线接到电源口,并且将电源跳线连接EXT-5V和PWR_5V(用连接J软件工程TAG和电脑的线供电时,需要将电源跳线跳到USBwindows11有必要升级吗_5V和PWR_5V),如图3.3所示,即可缓解单根JTAG到电脑线的供电不足问题。也可以尝试同时连接JATG端口,UART端口和电脑,接口用两根线缆同时供电。

图3.2 电源接口

图3.3 电源选择跳线

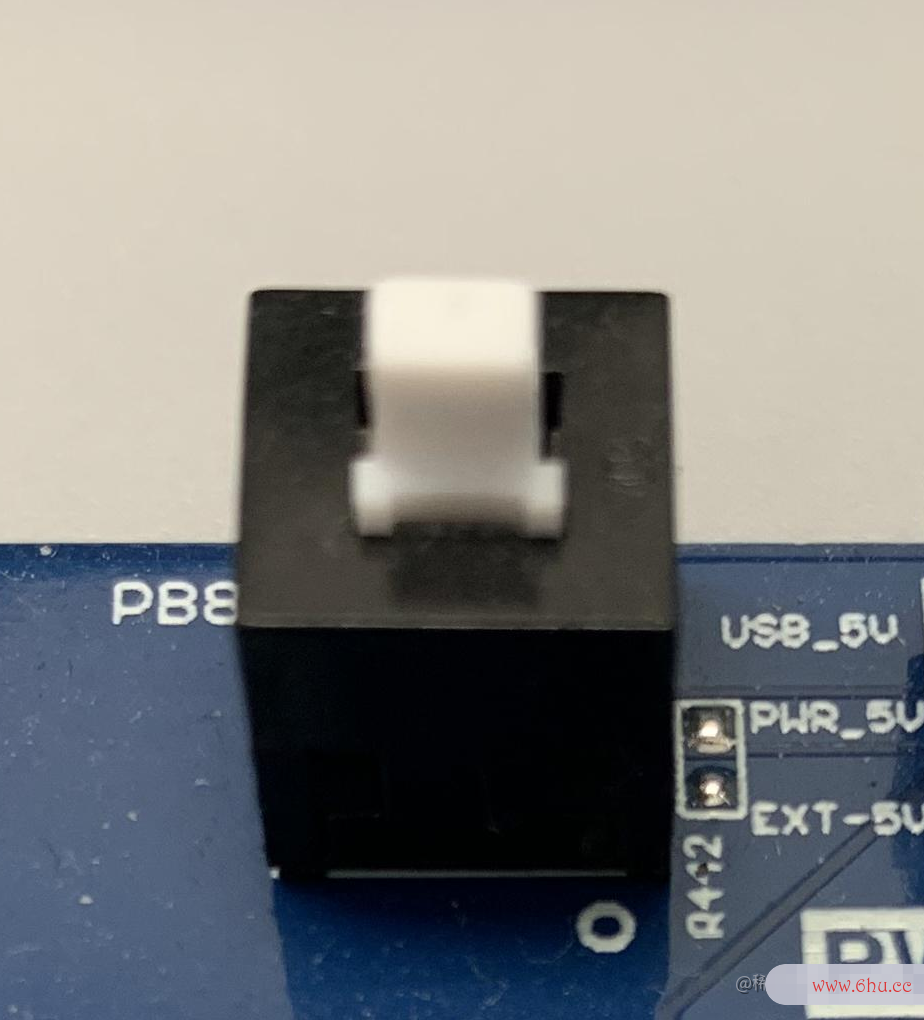

最后,注意测试英文在连接好P测试英文RX100-D和电脑后,需要将开发板的电源按钮按下启动。电源启动按钮如图3.4所示。

图3.4 电源启动按键

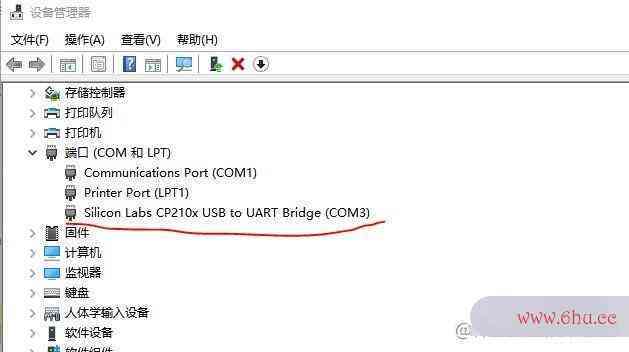

- 连接到UART接线后,在windows下的设备管理器下没有出现相应的端口。

正确的设备管理器发现UART接线的情况,如图3.5所示。但可能有少数情况下,UART的硬件无法被windows系统发现,这时,则需要重新安装CP210x的驱动程序,可以从Sil接口是什么icon Lab上官方网站上下载(点击这里到相应的界面)对应的驱动。

图3.5windows是什么意思 设备管理器中出现正常的UART接线

- Vivado错误Windows:ERROR: [Common 17-70] Application Exception: CORE_LOCATION mismatch

错误出现的步骤一般是在添加debug core后上板调试时,错误原因不明。Xilinx官方技术人员提供的解决方软件商店法都没有效果。实际有效的操作为关闭Vivado窗口,再次重新打开。

4.文章参考

[1] Xilinx官方论坛:www.xilinx测试工程师.com/support.htm…